74LS90功能比较多,不过我只选用了十进制的计数功能。

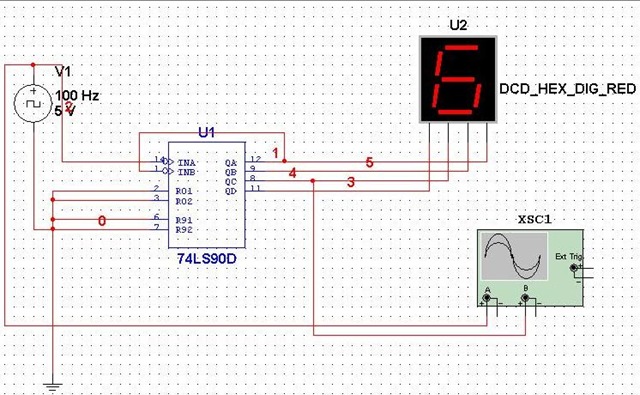

连线规则如下:

1.QA连INB,就可以构成十进制计数。这个是根据该TTL集成模块内部逻辑结构判断出来的,可以作为一种经验,不用多说。

2.两个置零端R0和两个置九端R9均接地,不让置零或置九。其实这四个引脚是用来测试整个集成电路是否正常的时候用的,方法很简单,R0(1) = R0(2) = 1同时R9(1) = R9(2) = 0数码管显示0,接着把置九端和置零端的电平互换,数码管显示9,则集成电路完好。

3.QA QB QC QD分别接入数码管的D C B A端口,检测计数

4.双踪示波器A端接时钟源,B端分别接QA QB QC QD,用以对比分频和占空比的情况。

经过Multisim10的仿真,数码管从0向上计数到9,再跳回到0,不断反复。

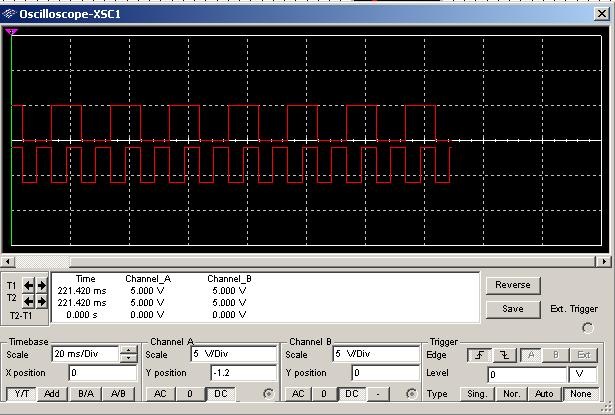

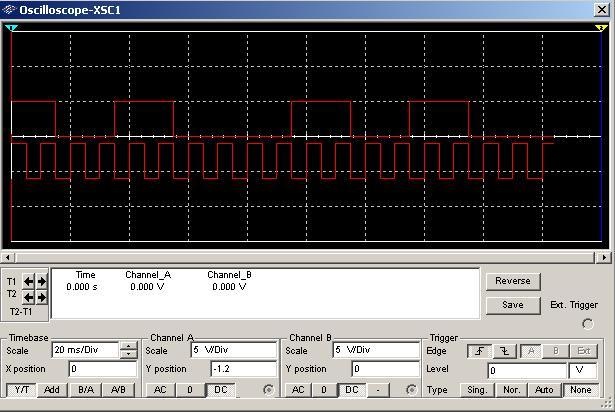

示波器观察到各端口和时钟源的分频情况如下

QA对时钟源进行了2分频,占空比为50%

QB对时钟源进行了四分频,但占空比有变换,至于为什么会这样,我也不知道,但是上星期在实验室搭线时却没发生这样的现象

QC QD都是十分频,占空比50%

在仿真和实际搭线的过程中发现,把示波器接上四个端口之后,整个计数频率会降低,数字跳变速度变慢。询问过实验室老师后发现,其实示波器内部有电阻,接到四个输出端后会改变整个电路的输出电阻,这样反馈再反馈作用下,整个计数频率会有变换